Intel's 0.09-micron Process - More Details Emerge

by Anand Lal Shimpi on August 13, 2002 4:02 AM EST- Posted in

- CPUs

Straining Silicon

The most interesting part of Intel's 90nm announcement today is the commitment to strained silicon technology. To understand the benefits of strained silicon you first have to understand some of the fundamental issues with transistors.

Simply put, you want transistors to be able to pass as much current as possible when they're switched on and to pass no current when they're switched off. Unfortunately we don't live in a perfect world and transistors don't always behave as they should. Technologies such as Silicon on Insulator (SOI) help stop current from flowing when it shouldn't (leakage current) and technologies such as Strained Silicon help increase the amount of current that's allowed to flow when it's needed (drive current).

We've already explained how Silicon on Insulator works and both AMD and Intel have committed to using the technology; AMD will be first to market with SOI through their Hammer parts, while Intel will introduce SOI with their 65nm process in 2005.

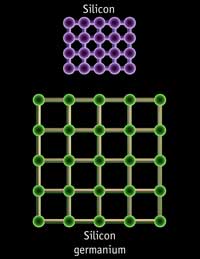

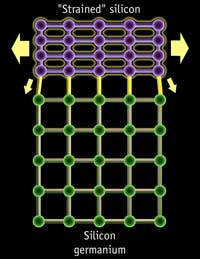

Strained Silicon works by effectively stretching the silicon in the channel region of the transistor. The engineers at Intel's fab facilities don't sit there and pull on both ends of the silicon in order to get it to stretch; rather they place the silicon on top of a substrate whose atoms are already spaced further apart than the silicon that needs to be stretched. The result of this is that the silicon atoms on top of the substrate will stretch to match the spacing of the substrate below, thus "stretching" the silicon in the channel.

|

|

|

Silicon

is "strained" by using a substrate of more widely spaced atoms

below the silicon channel of a transistor. (Images courtesy of IBM)

|

|

With more well spaced silicon atoms, electrons can now flow with less resistance in the channel meaning that more current can flow through the channel when needed. The end result is a 10 - 20% increase in drive current, or the current flowing through the channel of the transistor.

![]()

Intel claims that their Strained Silicon technology has no real downsides (unlike competing solutions) other than its 2% increase in manufacturing costs. Intel's 90nm process will make use of Strained Silicon technology to improve the performance of their 90nm transistors.

0 Comments

View All Comments